# P856M/P857M System Handbook

- ASYNCHRONOUS GENERAL PURPOSE BUS

- SINGLE CARD MICROPROGRAMMED CPU

- INTEGRATED CONSOLE CONTROL UNIT

- CYCLE SPEED OF 1.2 OR 0.7 MICROSECONDS.

- MEMORY MODULES OF 8 OR 16K WORDS

- MEMORY CYCLES INTERLEAVING

- MODULAR SYSTEM

- 16-BIT WORD ORIENTED

- 16 GENERAL PURPOSE REGISTERS

- MEMORY MANAGEMENT UNIT (P857M), 2K WORD PAGE SIZE

- FLOATING POINT PROCESSOR (P857M)

- PROGRAMMABLE REAL TIME CLOCK

- DIRECT, INDIRECT, INDEXED, INDEXED INDIRECT ADDRESSING

- 63 INTERRUPT LEVELS

- EXTERNAL REGISTER TRANSFERS.

- HARDWARE MULTIPLY/DIVIDE, DOUBLE LENGTH ARITHMETIC

- AUTOMATIC STACK HANDLING

- REAL TIME CLOCK (20 MS, MAINS)

- INTEGRATED V24 SERIAL CONTROL UNIT.

- POWER FAILURE DETECTION WITH AUTOMATIC RESTART

- MICRODIAGNOSTICS

- LOW AND HIGH SPEED DATA CHANNELS

- INTERFACES FOR INDUSTRIAL EQUIPMENT

- DATA COMMUNICATION

- POSSIBILITIES TO CONNECT ALL STANDARD PERIPHERALS

- SOFTWARE PACKAGE INCLUDES:

STAND ALONE SOFTWARE

BASIC AND BASIC REAL TIME MONITORS

DISC AND DISC REAL TIME MONITORS

MULTI APPLICATION MONITOR (P857M)

SMALL REAL TIME MONITOR

CASSETTE OPERATING MONITOR

MONITOR EXTENSION FOR DATA COMMUNICATION

ASSEMBLER, FORTRAN COMPILER, BASIC, FACT, LINKAGE EDITOR, OVERLAY LINKAGE EDITOR, CASSETTE EDITOR, UPDATE PACKAGE, LINE EDITOR, DEBUGGING PACKAGE, HARDWARE TEST PROGRAMS

P856M/P857M System Handbook

### A publication of

Philips Data Systems B.V. Marketing Group Small Computers Apeldoorn, The Netherlands

Publication number 5122 991 26932

April 1976

Copyright © by Philips Data Systems B.V. 1976 All rights strictly reserved. Reproduction or issue to third parties in any form whatever is not permitted without written authority from the publisher.

Printed in the Netherlands

This handbook is one of a series of manuals which covers all aspects of the P856M and P857M mini computer system. It is intended to provide general information with respect to the system in the form of short descriptions of the component units and peripheral devices which comprise the system.

Because of the flexibility of the system it is possible to include non-standard and customer designed equipment within any system and where such possibilities exist the connection facilities available have also been generally described. A user should however refer to the more detailed publications within the series before using such facilities.

Great care has been taken to ensure that the information contained in this manual is accurate and complete. Should a user, however, find any errors or omissions, or wish to suggest improvements, he is invited to write his comments on the sheet provided at the end of this book and send it to:

Manual Writing Small Computers at the address on the opposite page.

### **Table of Contents**

|                                                   |          |      |      |      |     |   |   |   |   |   |   |   |   |   |   |   | Page |

|---------------------------------------------------|----------|------|------|------|-----|---|---|---|---|---|---|---|---|---|---|---|------|

| Preface                                           |          |      |      |      |     |   |   |   |   |   |   |   | • | • | • | • | Ī    |

| List of Figures                                   |          | -    |      | -    |     |   |   |   |   |   |   |   |   | ٠ | - | - | VIII |

| Definitions and Abbreviations                     |          | -    | -    |      |     |   |   |   |   | - |   |   |   |   |   | - | X    |

| Introduction                                      |          |      |      |      | -   | - |   |   |   |   | - |   |   |   |   |   | ΧI   |

| Chapter 1 General                                 |          |      |      |      |     |   |   |   |   |   |   |   |   |   |   |   | 1-1  |

| The System                                        |          |      |      |      |     | - |   |   |   |   | - |   |   |   |   |   | 1-1  |

| Memories                                          |          |      |      |      |     |   |   |   | - |   |   |   |   |   | - |   | 1-2  |

| Interleaving                                      |          |      |      | -    |     |   |   |   | - |   | ٠ |   |   |   | • | ٠ | 1-3  |

| Control Panel                                     |          |      |      |      | -   |   |   |   |   |   | ٠ |   | - |   |   |   | 1-4  |

| General Specifications                            |          |      |      |      | •   | • | - | - |   |   |   |   | • | ٠ | • | • | 1-4  |

| Chapter 2 Hardware Structure                      |          |      |      |      |     |   |   |   |   |   |   |   |   | _ |   |   | 2-1  |

| Central Processing Unit                           |          |      |      |      |     |   |   |   |   |   |   | , |   |   |   |   | 2-1  |

| Arithmetic Unit                                   |          |      |      |      |     |   |   |   |   |   |   |   |   |   |   |   | 2-1  |

| P register                                        |          |      |      |      |     |   |   |   |   |   |   |   |   |   |   |   | 2-1  |

| The PSW register                                  | -        |      | -    | _    |     | _ |   |   |   |   |   |   |   | _ |   | , | 2-1  |

| The Scratchpad                                    |          |      |      |      |     |   |   |   |   |   |   |   |   |   |   |   | 2-2  |

| The L register                                    |          |      |      |      |     |   |   |   |   |   |   |   |   |   | _ |   | 2-4  |

| The M register                                    |          |      |      |      |     |   |   |   |   |   |   |   |   |   |   |   | 2-4  |

| The Q register                                    |          |      |      |      |     |   |   |   |   |   |   |   |   | , | , |   | 2-4  |

| The D multiplexer.                                | Ī        | •    | -    |      |     |   |   |   |   |   |   |   |   |   |   |   | 2-4  |

| The C multiplexer                                 | Ī        |      |      |      |     |   |   |   |   |   |   |   |   |   |   |   | 2-4  |

| The S register                                    |          | -    |      | _    | -   |   |   |   |   |   |   |   |   |   |   |   | 2-4  |

| The K register                                    |          |      |      |      |     |   |   |   | _ |   | _ | _ |   |   |   |   | 2-5  |

| Address Generator GA .<br>ROM Address Register RA | Ī        | Ī    |      | -    |     |   |   |   |   | Ċ |   |   |   |   |   |   | 2-5  |

| ROM Address Register RA                           |          | •    |      | •    | -   |   |   | _ |   |   |   |   |   |   |   |   | 2-5  |

| Control ROM and Micror                            | ).<br>). | era  | m    |      | -   |   |   |   |   |   |   |   | Ċ |   | · |   | 2-5  |

| Control and Data Flow.                            |          |      |      |      |     |   |   |   |   |   |   |   |   |   |   |   | 2-5  |

| Chapter 3 The Basic Word.                         |          |      |      |      |     |   |   |   |   |   |   |   |   |   |   |   | 3-1  |

| Data Format                                       | •        | •    | •    |      | -   | • | • | • | • | • | • | ٠ | + | ٠ | • | • | 3-2  |

| Data Format                                       | •        | •    | •    | •    | •   | • | ٠ | • | • | • | • | • |   | • | • | • | J-2  |

| Chapter 4 Memory                                  |          |      |      |      | ,   | , |   |   |   |   |   |   |   | , |   |   | 4-1  |

| Memory Addressing                                 | -        |      |      |      |     |   |   |   |   |   |   | • |   |   |   | ٠ | 4-3  |

| Chapter 5 Memory Manageme                         | mt       | IIn  | ie N | AN.  | 411 |   |   |   |   |   |   |   |   |   |   | _ | 5-1  |

| Description                                       | -11      | OII. | Tr Y | FALT | -0  | • | • | - | • | • | • | • | • | ٠ | • | • | 5-1  |

| Layout of segment table we                        | Ord      | ,    | •    | •    | •   | • | • | • | ٠ | • | • | ٠ | • | • |   | • |      |

| Page Fault Handling                               |          |      |      |      |     |   |   |   |   |   |   |   |   |   | • | • | 5-3  |

| rage Fault Flamuillik                             |          |      | •    | -    |     |   | • |   | • | - |   | • | - |   | 7 | - |      |

| Chapter 6 Floating Point Process                             | ior i | rri | •   | • | • |   | • | • | - | • |   |   | ٠ | • | • | 0-1        |

|--------------------------------------------------------------|-------|-----|-----|---|---|---|---|---|---|---|---|---|---|---|---|------------|

| Introduction                                                 |       | ٠   | -   | ٠ | - |   | - | - | - | - |   |   | - | • | - | 6-1        |

| Operation                                                    |       | ٠   | -   | ٠ | • | • | - |   | - | - |   | - | - | ٠ | - | 6-1        |

| Classing Doint Format                                        | _     | _   |     |   |   |   |   |   | - | _ |   | _ | _ |   | _ | 6-3        |

| Floating Point Instructions                                  | -     | ٠   | •   | • | ٠ | • | • | ٠ | - | - | ٠ | • | • | • | • | 6-4        |

| Chapter 7 Instructions                                       |       |     |     |   |   |   |   |   |   |   |   |   |   |   |   | 7-1        |

| Instruction Formats                                          |       |     |     |   |   |   |   |   |   |   |   |   |   |   |   | 7-1        |

| Forming the Operand                                          |       |     |     |   |   |   |   |   |   | _ |   |   |   |   |   | 7-4        |

| Instruction Timing                                           |       |     |     |   |   |   |   |   | i | _ | _ |   | _ |   |   | 7-5        |

| Trap Action                                                  |       |     |     |   |   |   | _ |   |   | _ | - |   |   | · | Ċ | 7-5        |

| The Instruction Set                                          |       |     |     |   |   |   | _ |   |   | _ |   |   | Ĺ |   | - | 7-5        |

| Load/Store Instructions                                      | •     | •   | •   | • | • | • | • | • | • | • | • | • | ٠ | • | • | 7-6        |

| Arithmetic Instructions .                                    | -     | •   | •   | • | • |   | • | ' | • | • | • | • | • | • | • | 7-6        |

| Logical Instructions                                         | -     | •   | •   | • | ٠ | • | • | • | • | • | • | • | • | • | • | 7-8        |

| Character Handling Instruct                                  | ian:  | ,   | '   | • | • | • | • | • | • | • | • | • | • | • | - | 7-8<br>7-8 |

| Branch Instructions                                          | iQH;  | · · | •   | • | • | • | • | • | • | ٠ | • | • | • | - | - |            |

| Shift Instructions                                           | -     | ,   | •   | • | • | • | • | • | • | ٠ | • | • | • | - | • | 7-8        |

| Shift Instructions                                           | •     | •   | •   | ٠ | • | • | ٠ | • | - | ٠ |   | - | • | • | ٠ | 7-9        |

| Control Instructions                                         |       |     |     |   |   |   |   |   |   |   |   |   |   |   |   | 7-9        |

| Input/Output Instructions .                                  | ٠     | •   | •   | ٠ |   | - | • | - | - | • | • | ٠ | • | - | ٠ |            |

| External Transfer Instruction                                | ıs.   | •   | ٠   | ٠ | • | - | • | - | • | • | • | • | • | • | ٠ | 7-10       |

| Move Table Instructions                                      | •     |     |     | ٠ | • | - |   |   | • |   |   | ٠ |   | - |   | 7-10       |

| Chapter 9 General Purpose Bus                                |       |     |     |   |   |   |   |   |   |   |   |   |   |   |   | 9-1        |

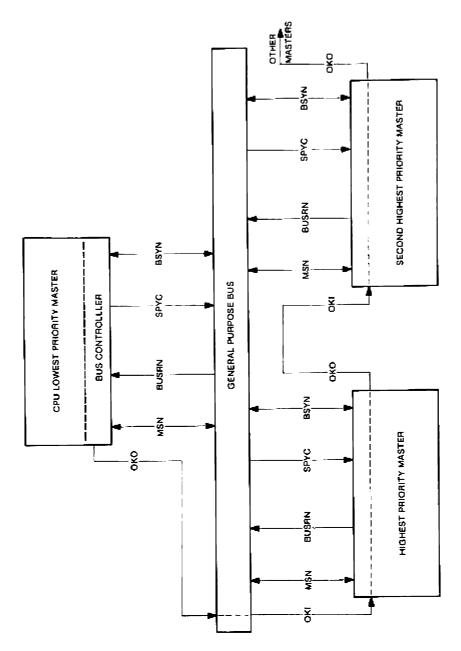

| Bus Control Functions                                        | •     | •   | •   | • | • | • | • | • | • | • | • | • | - | - | - | 9-1        |

| Priority Chain                                               | •     | •   | •   | • | • | ٠ | • | • | • | • | • | ٠ | • | • | • | 9-2        |

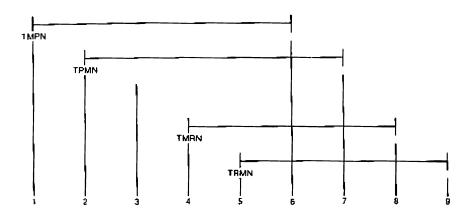

| Data or Command Exchanges                                    | •     | •   | •   | • | • | • | • | • | ٠ | - | • | ٠ | • | • | • | 9-2        |

| Data or Command Exchanges .<br>Timing Control                | •     | •   | •   | • |   | • |   | • | • | • | • | ٠ | • | • | • | 9-2<br>9-5 |

| Interrupt Handling                                           | •     | ٠   | •   | • | • | • | - | • | • | • | • | • | ٠ | • | • |            |

| Interrupt Handling                                           | -     | -   |     | • | - | • | • | • | 1 | • | • | • | • | • | • | 9-5        |

| Rue Signat Linne                                             | -     | ٠   | •   | • | • | • | • | • | • | • | ٠ | - | ٠ | • | - | 9-5        |

| Miscellaneous Functions Bus Signal Lines Bus Control Signals | •     | ٠   | •   | • | • | ٠ | • | ٠ | • | - | ٠ | - | - | • | • | 9-5        |

| Data or Command Euchana                                      |       |     |     | • | ٠ | • | • | • | - | - |   | - | - | • | - | 9-5        |

| nava or community exchang                                    | (C 3) | щп  | 215 | - |   | - | - | - |   | - |   |   |   |   |   | 9-6        |

| Bus Data Lines                                               | •     | ٠   | •   | • | ٠ | • | - | ÷ | • | • | ٠ | • | • | • | • | 9-7        |

| Missallaneous Claud                                          | -     | •   | •   | - | • | • | - | • | • | ٠ |   | • | • | • | ٠ | 9-8        |

| Bus Interrupt Lines                                          | -     |     | -   | - | ٠ | - | ٠ | • |   | • |   |   | • | 4 |   | 9-8        |

| Chapter 10 Interrupt System                                  |       |     |     |   |   |   |   |   |   |   |   |   |   |   |   |            |

| Organization                                                 | •     | •   | •   | • | • | • | • | • | • | • | • | - | • | • | ٠ | 10-1       |

| Organization Operation of the Priority System                | ٠.    | -   | -   | • | • | ٠ | • | • | ٠ | • | • | ٠ | • | • | ٠ | 10-1       |

| Interrupt Action                                             | 11 -  | •   | •   | - | • | • | ٠ | • | • | • | ٠ | • |   | • | ٠ | 10-1       |

| Interrupt Action                                             | -     | •   | -   | • | • | • | • | • | • | • |   | • | • | • | • | 10-3       |

| Stacking                                                     | •     | ٠   | •   | ٠ | ٠ | ٠ | - | ٠ |   | - | - | • | - | ٠ | • | 10-7       |

| Chapter 11 Input/Output                                      |       |     |     |   |   | - |   |   |   |   |   |   |   |   |   | 11-1       |

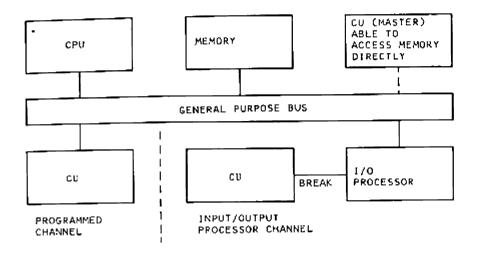

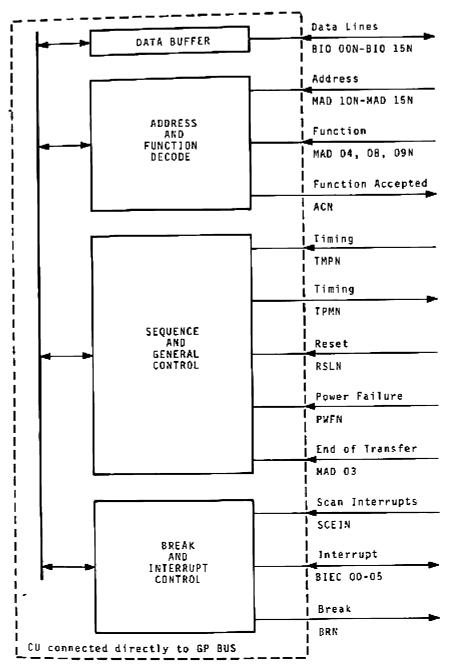

| Control Units.                                          | 1-2    |

|---------------------------------------------------------|--------|

| Control Units Connected Directly to the GP Bus          | 1-4    |

| Definition of Units                                     | 1-5    |

| Programmed Channel                                      | 1-7    |

| Wait Mode                                               | 1-7    |

| Interrupt Mode                                          | 1-7    |

| Commands and Responses                                  | 1-8    |

| Commands and Responses                                  | 1-8    |

| Input/Output Processor Channels                         | 1-12   |

| Organization 1                                          | 1-12   |

| Organization                                            | 1_14   |

| Control and Data Flow                                   | 1 10   |

| Direct Memory Access                                    | 1-10   |

| Transfers CPU/External Registers                        | . 1-10 |

|                                                         | ~ .    |

| Chapter 12 Control Panels                               | .Z-1   |

| Full Control Panel                                      | .2-1   |

| Safety Key Switch                                       | 2-1    |

| Display Lamps                                           | 2-2    |

| Data Switches                                           | 2-2    |

| Register Address Switches                               | 12-2   |

| Control Buttons                                         | 2-2    |

| Mode Buttons                                            | 12-3   |

| Service Buttons                                         | 2-4    |

| Transportable Panel                                     | 2-4    |

| Minipage                                                | 2-4    |

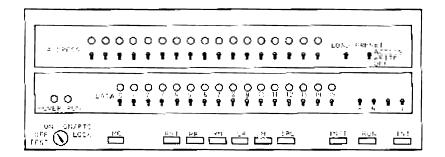

| Extended Control Panel                                  | 12-5   |

| Dienlay Lamns                                           | 2-5    |

| Address Switches                                        | 12-5   |

| Load Switch                                             | 12-5   |

| Load Switch                                             | 12.5   |

| Paul Marsant Broadure                                   | 12-5   |

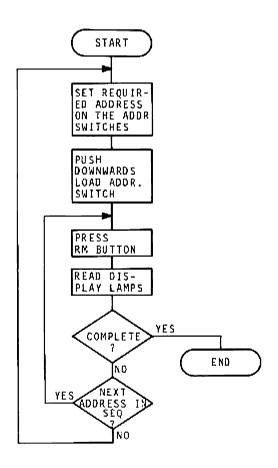

| Read Memory Procedure                                   | 12-0   |

| Load Memory Procedure                                   | 12-0   |

| 61 . IA 15 I A 15 I A                                   | 12.1   |

| Chapter 13 Basic Loading and Operating                  | 13-1   |

| Program Loading                                         | 13-1   |

| Initial Program Loader                                  | 13-1   |

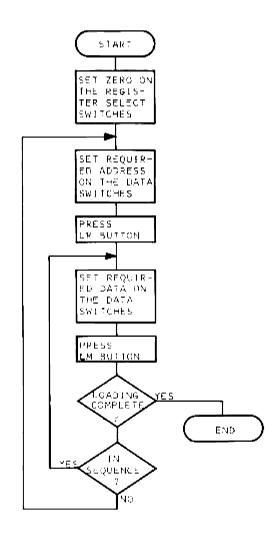

| Load Memory (Full Control Panel)                        | 13-6   |

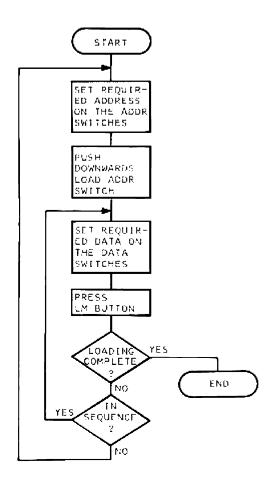

| Load Memory (Extended Control Panel)                    | 13-7   |

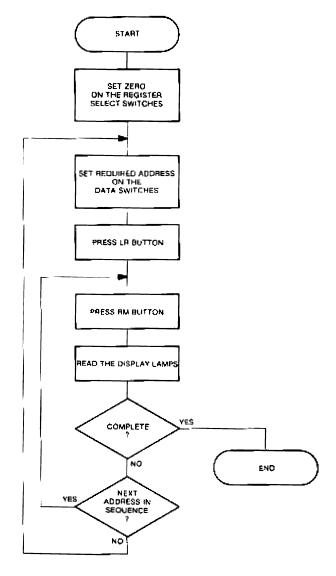

| Read Memory (Full Control Panel)                        | 13-8   |

| Read Memory (Extended Control Panel)                    | 13-9   |

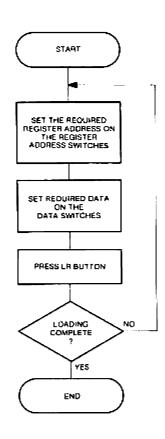

| Load Register                                           | 13-10  |

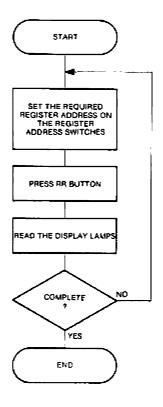

| Read Register                                           | 13-11  |

|                                                         |        |

| Chapter 14 Additional Standard Features                 | 14-1   |

| Power Failure-Automatic Restart                         | 14-1   |

| Real Time Clock                                         | 14-2   |

| 1000 - 1000 Cidon , , , , , , , , , , , , , , , , , , , | _      |

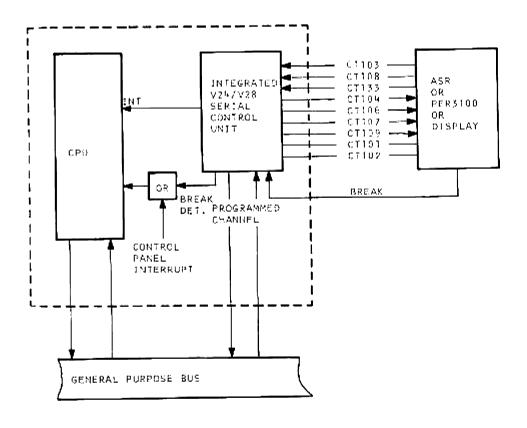

| Integrated V24/V28 Serial Contr  | roi  | U   | nıt | ٠    | •   | •    | •  | •   | ٠  |    | •   | -  | -   | -   | ٠ | • | 14-2  |

|----------------------------------|------|-----|-----|------|-----|------|----|-----|----|----|-----|----|-----|-----|---|---|-------|

| Break Feature                    | -    | -   |     |      | •   |      | ٠  | •   | ٠  | •  | •   | ٠  | •   | •   | + | - | 14-4  |

| Microdiagnostics                 | -    |     |     |      |     | -    |    | •   | -  |    |     | ٠  | •   | •   |   | • | 14-7  |

| Test Procedures                  |      |     | •   | ٠    | -   |      |    |     |    |    |     |    |     |     | • | - | 14-7  |

| Detection Of Privileged Instruc  | tio  | ПS  |     | -    |     |      |    | •   |    |    |     |    | •   | -   |   |   | 14-10 |

| System Mode                      | -    | -   |     |      |     |      |    |     |    |    |     |    | -   |     |   |   | 14-10 |

| User Mode                        | •    |     | •   | •    | •   | -    | ٠  | •   | •  | •  | •   | ٠  | •   |     | ٠ | • | 14-10 |

| Chapter 15 Data Communication    | HB 1 | and | D   | igi  | tel | OF   | Aı | nai | og | ln | pui | /C | )ut | put | ì |   | 15-1  |

| Data Communication               |      |     | -   |      | -   |      |    |     |    |    |     |    |     |     |   |   | 15-1  |

| Digital Input/Output System.     |      |     |     |      |     |      |    |     |    |    |     |    |     |     |   |   | 15-2  |

| Modular I/O System               | •    | •   | •   | •    | •   | •    | •  | •   | •  | •  | •   | ٠  | -   |     |   | - | 15-2  |

| Chapter 16 Cabinets, Installatio | n 8  | and | In  | ıter | fac | cing | 2  |     | ,  |    |     |    |     |     |   |   | 16-1  |

| Cabinets                         |      |     |     |      |     | . '  |    | _   |    | _  | _   |    |     | _   |   | _ | 16-1  |

| Mounting Boxes and Equipmen      | nt . | Sh  | els | es.  | _   |      |    | _   |    | _  | -   | ·  | -   |     | • | • | 16.1  |

| M1 Mounting Box                  |      |     |     |      |     |      |    |     |    |    |     |    |     |     |   |   |       |

| M4 Mounting Box                  |      | _   |     |      | -   | -    |    | -   |    | •  | •   | •  | •   |     | • | • | 16.3  |

| M4M Mounting Box                 |      | -   |     |      | -   |      |    | •   |    | •  |     | •  |     | •   | • | • | 16.3  |

| M5M Mounting Box                 | •    | •   | •   | •    | •   | •    | •  | •   | •  | •  | ٠   | •  | •   | •   | • | • | 16.4  |

| Equipment Shelf                  | •    | •   | •   | •    | •   | •    | •  | •   | •  | •  | ٠   | •  | -   | •   | • | ٠ | 16.5  |

| Interconnection between I        | ln:  | ite | •   | •    | •   | •    | •  | •   | •  | •  | ٠   | •  | -   | •   | • | • | 16.5  |

| Installation                     | J    |     | •   | •    | -   | •    | •  | •   | •  | •  | •   | •  | -   | •   | • | ٠ | 16.5  |

| Electrical Supplies              | •    | •   | •   | •    | •   | •    | -  | •   | •  | •  | •   | •  | •   | •   | • | • | 10-3  |

| Environmental Control .          | •    | •   | •   | •    | •   | •    | •  | •   | •  | •  | •   | •  | •   | •   | • | • | 10-2  |

| Safety                           | •    | •   | •   | •    | •   | •    | •  | •   | •  | •  | •   | •  | •   | •   | • | • | 10-0  |

| Interfacing                      | •    | •   | •   | •    | •   | •    | •  | •   | •  | ٠  | •   | •  | •   | •   | ٠ | • | 10-0  |

|                                  | •    | •   | •   | •    | •   | •    | •  | •   | •  | •  | •   | •  | ٠   | •   | • | ٠ | 10-0  |

| Chapter 17 Peripheral Equipme    | ot   |     |     |      |     |      | ٠  | -   |    |    |     |    |     |     |   |   | 17-1  |

| Standard Peripheral Equipment    | ٠    | -   | •   |      | -   | ٠    | •  | •   | •  | •  | •   | •  | •   | ٠   | • | • | 17-1  |

| Power Supplies                   | •    | -   | •   | •    | •   | ٠    | •  | •   | •  | •  | •   | •  | •   | •   | ٠ | • | 17-2  |

| Connection to the System         | •    | •   | ٠   | •    | •   | ٠    | •  |     | •  |    | •   |    | •   | ٠   | • | • | 17-2  |

| Control Units.                   | •    | •   | •   | •    | •   | •    | •  |     | •  |    | •   | •  | •   | •   | • | • | 17-2  |

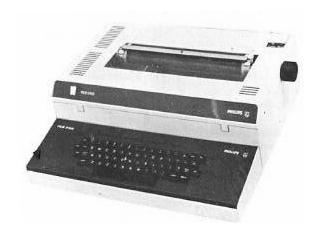

| Input/Output Typewriters         |      |     |     |      | •   |      |    | ٠   | •  | •  | ٠   |    | -   | •   |   | - | 17-4  |

| Punched Tape Equipment           |      | •   |     | •    | •   | •    |    | •   |    |    | ٠   |    | -   | ٠   |   | - | 17-9  |

| Card Reader                      |      |     |     |      |     |      |    |     |    |    |     |    | -   |     |   | - | 17-13 |

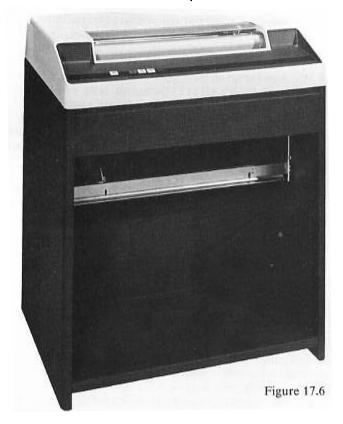

| Line Printers                    |      |     |     |      |     | +    |    |     |    |    | -   |    | -   | ٠   |   |   | 17-15 |

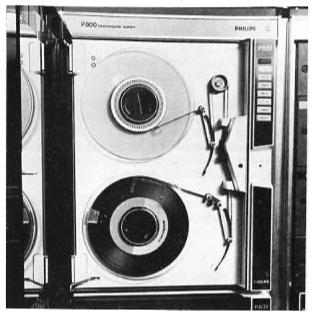

| Magnetic Tape Equipment.         |      | _   |     | _    | _   |      | _  | _   | _  | _  | _   |    | _   | _   | _ | _ | 17-19 |

| Magnetic Disc Equipment.         |      | _   |     | _    | _   |      | _  | _   |    | _  | _   |    | _   | _   |   | _ | 17-24 |

| Display Equipment                |      | -   | •   | •    | -   |      | •  | •   |    |    | •   |    | •   | •   |   | • | 17-28 |

| Chapter 18 Software              |      |     |     |      |     |      |    |     |    |    |     |    |     |     |   |   | 18-1  |

| Condoi Programs                  |      | _   |     | _    | _   |      |    |     |    |    |     |    |     |     |   |   | 12.7  |

| pasic Operating Monitor.         |      | _   |     |      |     |      |    |     |    |    |     |    |     |     |   |   | 12.7  |

| Basic Real Time Monitor          |      | -   | •   | •    | •   | •    | •  | -   | ٠  | •  | •   | •  | •   | •   | • | • | 10-7  |

| Disc Operating Monitor.       |    | , |   |   |   |   |   |   |   |   |   |   |   | - |   | - | 18-8  |

|-------------------------------|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-------|

| Disc Real Time Monitor.       |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 18-8  |

| Cassette Operating Monitor    | ۲. |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 18-8  |

| Small Real Time Monitor       |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 18-9  |

| Multi Application Monitor     | ٠. |   |   |   |   |   |   |   | , | - |   |   |   |   | _ |   | 18-9  |

| DATEM                         |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 18-10 |

| BSC                           |    |   |   |   |   |   |   |   |   |   |   |   |   | , |   |   | 18-11 |

| Processing Programs           |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 18-11 |

| Assemblers                    | ·  | - | Ċ | - |   |   |   | Ċ | _ |   |   | _ | _ |   |   |   | 18-11 |

| FORTRAN Compilers             | •  | • | • | • | ٠ | • | • |   | • | • |   |   | _ | _ | _ |   | 18-11 |

| Linkage Editor                | •  | • | • | • | • | • | • | ٠ | • | • | • | Ī | - |   | - |   | 18-12 |

| Overlay Linkage Editor        | •  | - | • | • | ٠ |   | • | • | • | • | • | • | · | • | - |   | 18-12 |

| Service and Utility Programs. | •  | • | • | • | ٠ |   | - | • | • | • | • | • | • | • | - | • | 18-17 |

| Debugging                     | •  | • | • | • | - | • | • | • | ٠ | • | ٠ | • | • | • | • | ٠ | 18-17 |

| Debugging                     | •  | • | • | • | ٠ | • | - |   | - | - |   | • | • | • | • | • | 10-12 |

| Update                        |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |       |

| Line Editor                   |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |       |

| Cassette Update               |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |       |

| Utility Programs              |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |       |

| BASIC                         |    |   |   |   | • |   |   | - |   |   | - |   |   | ٠ | • | - | 18-13 |

| CACT                          |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 10 14 |

Appendix 1 Peripheral Manufacturers Index

## **List of Figures**

### Index

| Figure | e                                                          |     |   |   |   |   |   |   |   |   | page  |

|--------|------------------------------------------------------------|-----|---|---|---|---|---|---|---|---|-------|

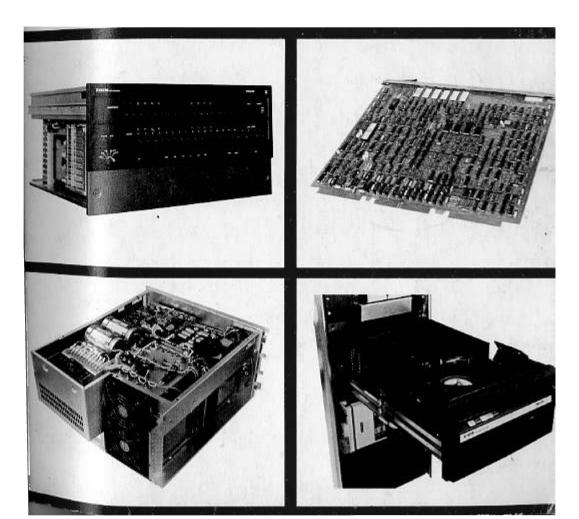

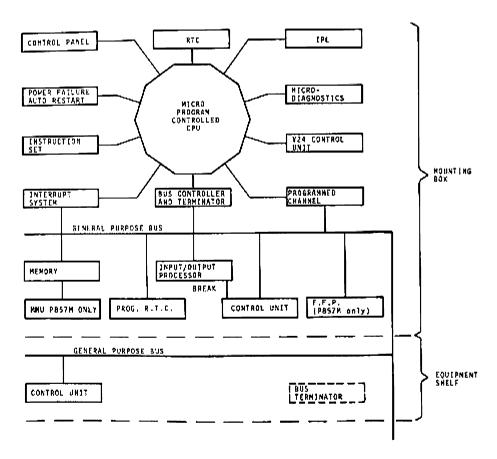

| 1.1    | System Main Components                                     |     | • | • |   | • |   |   |   |   | 1-2   |

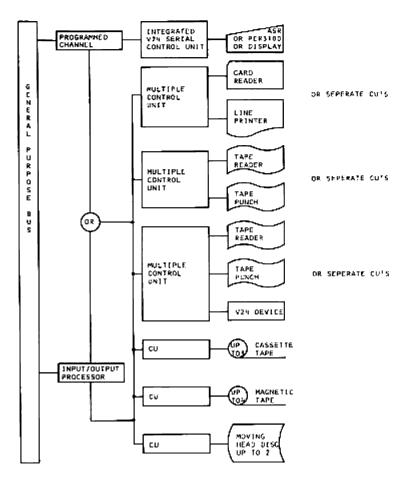

| 1.2    | Survey of peripherals and their control units              |     |   |   |   |   |   |   |   |   | 1-3   |

| 2.1    | General structure of cpu                                   |     | • | • |   |   |   |   |   |   | 2-2   |

| 2.2    | General structure of cpu.  Data flow in data handling unit |     |   |   | ٠ |   | - |   | - |   | 2-3   |

| 4.1    | Operation of memory in character mode.                     |     | - |   |   | - | - |   | - | - | 4-1   |

| 4.2    | Layout of words and characters in memory                   |     |   |   |   |   |   |   |   |   |       |

| 5.1    | MMU operation                                              |     | , |   |   | , | - |   |   |   | 5-2   |

| 6.1    | Connection of Floating Point Processor                     |     |   |   |   |   |   |   |   |   | 6-1   |

| 6.2    | Floating Point Processor                                   |     |   |   |   |   |   |   |   |   | 6-2   |

| 7.1    | Layout of instruction formats                              |     |   |   |   |   |   |   |   |   | 7-2   |

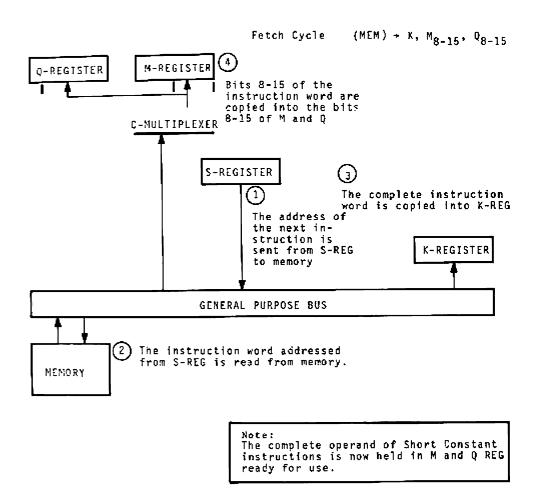

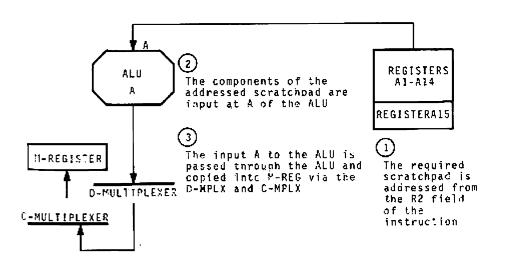

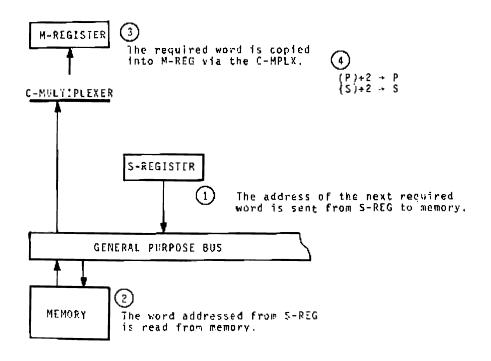

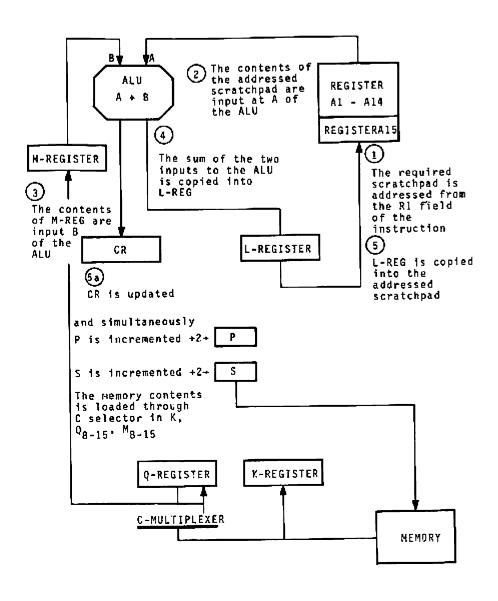

| 8.1    | Instruction Microprogram                                   |     |   |   |   |   |   |   |   |   | 8-2   |

| 8.2    | Microprogram Addressing routine                            |     |   |   |   |   |   |   |   |   | 8-3   |

| 8.3    | Accessing an instruction                                   |     |   |   |   |   | - |   |   |   | 8-4   |

| 8.4    | Addressing cycle (T1) (T3)                                 |     |   |   |   |   |   |   |   | - | 8-5   |

| 8.5    | Addressing cycle (T2) (T4-T7)                              |     |   |   |   |   |   |   |   |   | 8-6   |

| 8.6    | Execute cycle                                              |     |   |   |   |   |   |   |   |   |       |

| 9.1    | Connection of standard units to the Bus.                   |     |   |   |   |   |   |   | , |   | 9.1   |

| 9.2    | Bus priority and selection system                          |     |   |   |   |   |   |   |   |   |       |

| 9.3    | Exchange example                                           |     |   |   |   |   |   |   |   |   |       |

| 10.1   | Diagram of interrupt sequence                              |     |   |   |   |   |   |   |   |   |       |

| 11.1   | Units concerned with transfers                             |     |   |   |   |   |   |   |   |   |       |

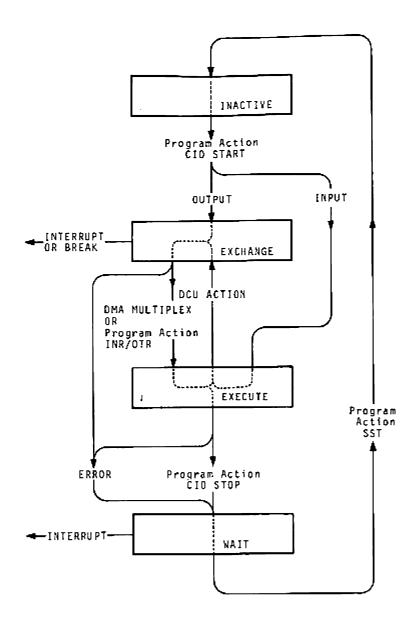

| 11.2   | Four states of standard control unit .                     |     |   |   |   |   |   | _ |   | _ | 11-3  |

| 11.3   | Signal exchange                                            |     |   |   |   |   |   |   |   |   | 11-6  |

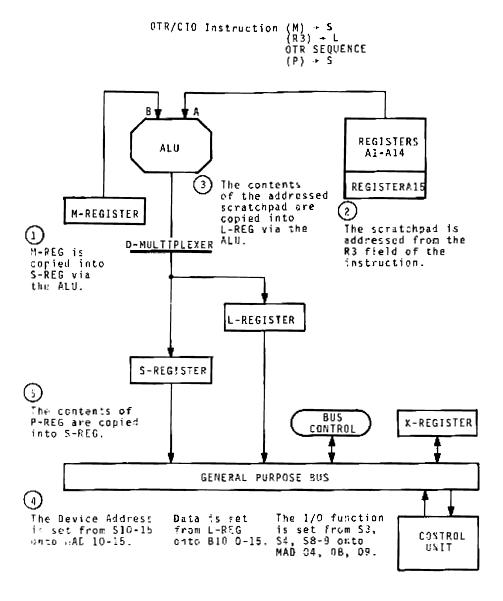

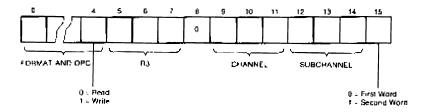

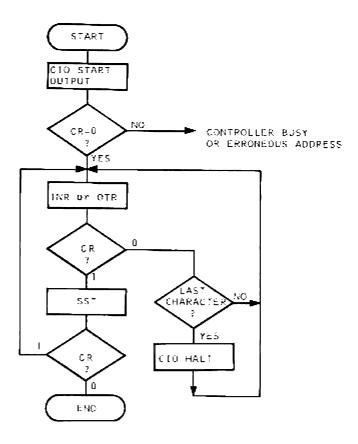

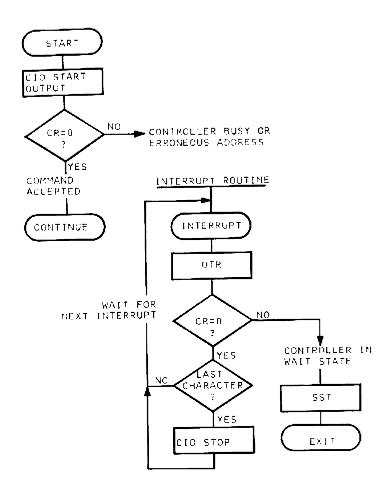

| 11.4   | OTR/CIO Instruction flow                                   | -   |   |   | • |   |   |   |   |   | 11-9  |

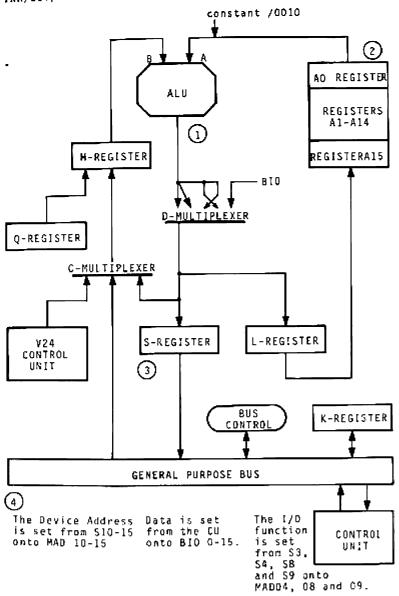

| 11.5   | INR/SST/TST Instruction flow                               | -   |   |   | - | Ċ | Ī | Ī |   |   | 11-10 |

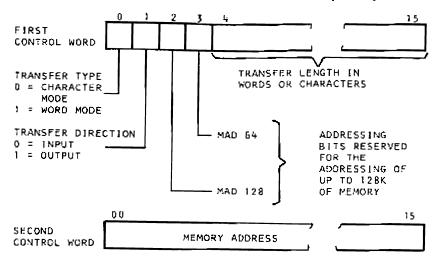

| 11.6   | I/O Processor control words                                |     |   |   |   |   |   |   |   |   |       |

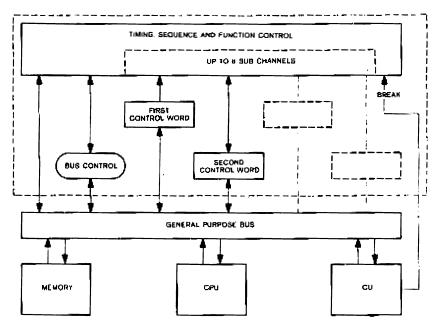

| 11.7   | I/O Processor within the system                            | -   |   | • | - | • | • |   |   | - | 11-13 |

| 11.8   | Read/Write External Register Layout                        | •   | • | • | - | · | • | • | · | • | 11-14 |

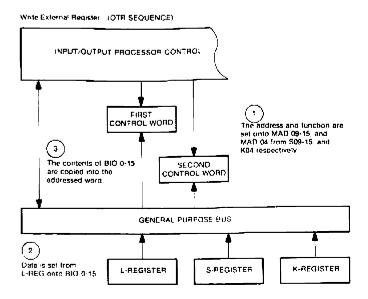

| 11.9   | WER instruction flow                                       | •   | • | • | • | • | • | • | • | • | 11-14 |

| 11.10  | Exchange action                                            | •   | • | • | ٠ | • | • | Ī | Ċ | • | 11.16 |

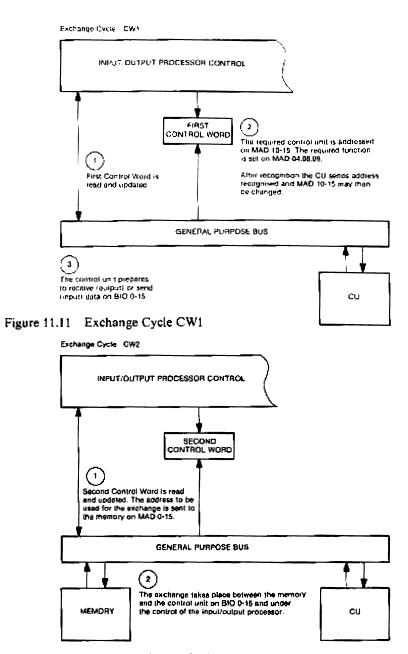

| 11.11  | Exchange cycle CW1                                         | •   | • | • | • | • | • | • | • | • | 11.17 |

| 11.12  | Exchange cycle CW2                                         | -   | • | • | • | ٠ | • | • | • | • | 11-17 |

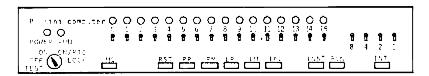

| 12.1   | Full Control Panel                                         | •   |   | • | - | • | ٠ | • | ٠ | • | 12-1  |

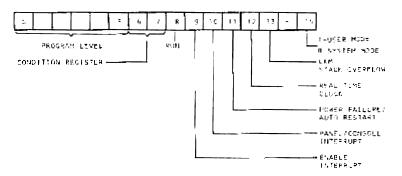

| 12.2   | Display of status                                          | •   | • | • | - | - | • | • | ٠ | • | 12.7  |

| 12.3   | Display of status                                          | •   | • | • | - |   | • | • | ٠ | • | 12.2  |

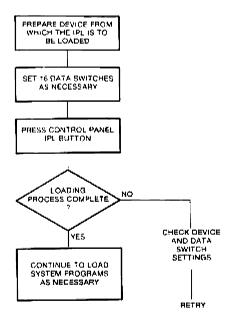

| 13.1   | Loading the IPL                                            | •   | ' | • | • | • | • | - | ٠ | • | 13.3  |

| 13.2   | Load data in memory (full control panel)                   | -   | • | • | - | ٠ | • | • | ٠ | ٠ | 10-3  |

| 13.3   | Load data in memory (extended control paner):              | .1\ | • | - | ٠ | • | - | ٠ | ٠ | • | 13-4  |

|        |                                                            |     |   |   |   |   |   |   |   |   |       |

| 13.4  | Read memory (full control panel)         |   |   |   |  |   |   |   | 13-6          |

|-------|------------------------------------------|---|---|---|--|---|---|---|---------------|

| 13.5  | Read memory (extended control panel)     |   | ٠ |   |  |   |   |   | 13-7          |

| 13.6  | Load register                            |   |   |   |  |   |   | - | 13-8          |

| 13.7  | Read register                            |   |   | - |  | - |   |   | 13-9          |

| 14.1  | Integrated serial control unit           | - |   |   |  |   |   |   | 14-3          |

| 14.2  | Wait mode                                |   |   |   |  |   |   |   | 14-5          |

| 14.3  | Interrupt mode                           |   |   |   |  |   |   |   | 14-6          |

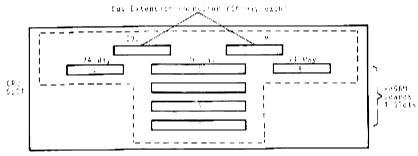

| 16.1  | M1 Mounting Box backplane arrangeme      |   |   |   |  |   |   |   | 16-1          |

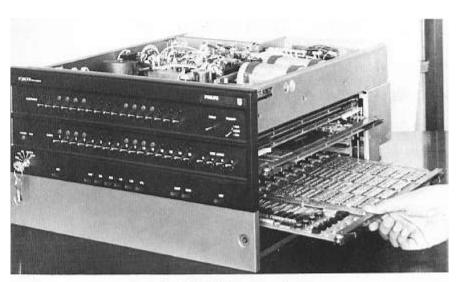

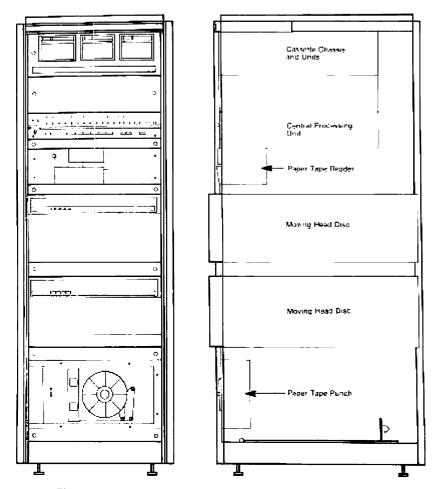

| 16.2  | Example of equipment mounted in cabin    |   |   |   |  |   |   |   | 16-2          |

| 16.3  | M4 Mounting Box side view                |   |   |   |  |   |   |   | 16-3          |

| 17.1  | I/O Typewriter ASR33                     |   |   |   |  |   |   |   | 17-4          |

| 17.2  | PER3100 Matrix printer                   |   |   |   |  |   |   |   | 17-6          |

| 17.3  | Punched Tape Reader                      |   |   |   |  |   |   |   | 17-9          |

| 17.4  | Tape Punch                               |   |   |   |  |   |   |   | 17-11         |

| 17.5  | Card Reader                              |   |   |   |  |   |   |   | 17-13         |

| 17.6  | X1415 Matrix Line Printer                |   |   |   |  |   |   |   | 17-15         |

| 17.7  | Line Printer                             |   |   |   |  |   |   |   | 17-17         |

| 17.8  | Magnetic Tape Unit                       |   |   |   |  |   |   |   | 17-19         |

| 17.9  | Cassette Drive Unit                      |   |   |   |  |   |   |   | 17-22         |

| 17.10 | X1215 Moving Head Disc Unit              |   |   |   |  |   |   |   | 17-24         |

| 17.11 | P825-007 Moving Head Disc Unit           |   |   | _ |  |   |   |   | 17-2 <i>6</i> |

|       | Display                                  |   |   |   |  |   |   |   | 17-26         |

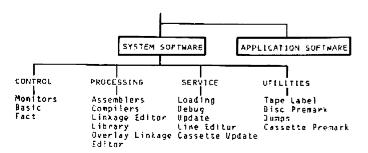

| 18.1  | Standard System Software and Application |   |   |   |  |   |   |   | 18-1          |

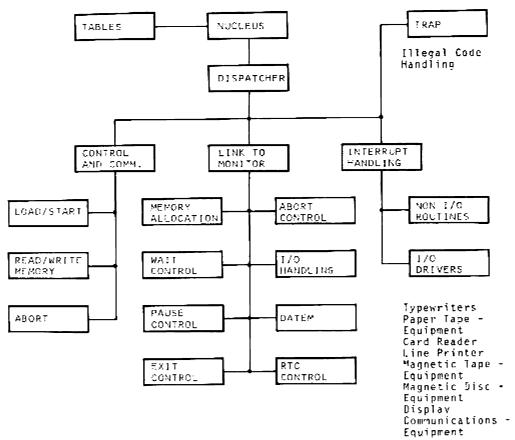

| 18.2  | Modular structure of monitor             | , |   |   |  |   | _ |   | 18-2          |

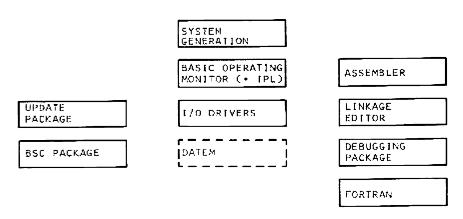

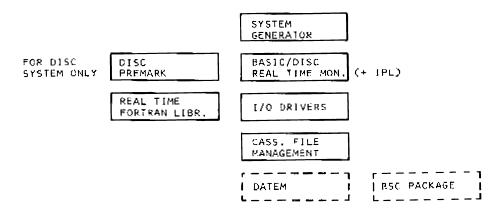

|       | Stand Alone software                     |   |   |   |  |   |   |   | 18-3          |

|       | Software for Basic Operating System      |   |   |   |  |   |   |   | 18-3          |

|       | Software for Basic and Disc Real Time Sy |   |   |   |  |   |   |   | 18-4          |

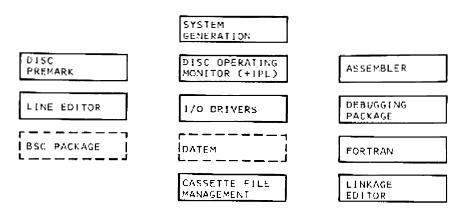

|       | Software for Disc Operating System       |   |   |   |  |   |   |   | 18-5          |

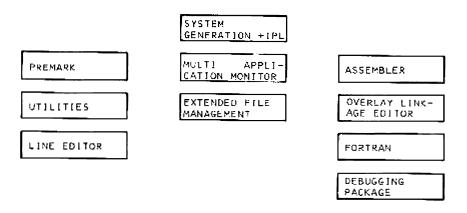

|       | Software for Multi Application System    |   |   |   |  |   |   |   | 18-5          |

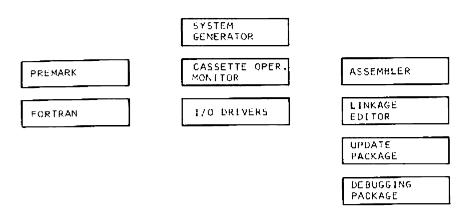

|       | Software for Cassette Operating System   |   |   |   |  |   |   |   | 18-6          |

| 18.9  | Software for Small Real Time Monitor .   |   |   |   |  |   |   |   | 18-6          |

Cabinet

- The basic structure containing 19" racks

Rack

- The structure within the cabinet to which rack mounted units may be secured.

Rasic Cabinet

- A cabinet in which the CPU is mounted.

Extension Cabinet

- A cabinet containing system equipment other than the

Mounting Box

- The rack in which the CPU is plugged.

Equipment Shelf - The rack in which system equipment other than the CPU

is plugged.

Standard

- One which is listed in the Catalogue.

Device Unit or Package

Microdiagnostics - A microprogram standard available on the CPU board, which tests panel drivers, data path, bus dialogue and me-

mory.

Character

One half-word: 8 bits.

MSI

- Medium Scale Integration.

LSI

Large Scale Integration.

TTI.

- Transistor to Transistor Logic.

ROM

Read Only Memory.

PROM

- Programmable Read Only Memory.

MOS

- Metal Oxide Semi-conductor.

IPL

- Initial Program Loader.

GP BUS

- General Purpose Bus.

MMU

Memory Management Unit.

FPP

- Floating Point Processor

The P856M and the P857M mini computers are general purpose digital processors designed for industrial and scientific applications.

These computers are the newest members of the successful P800M series family which were placed in all Western-European countries as well as in the United States and Japan.

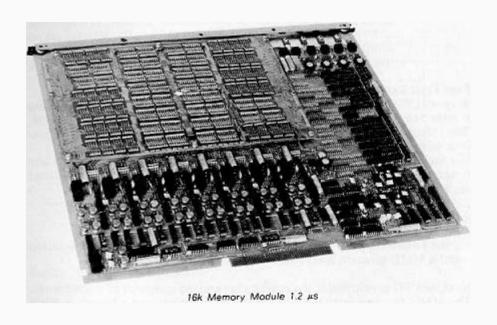

The P856M and the P857M are fast, compact and easy to interface thanks to the asynchronous General Purpose Bus around which all I/O facilities are centered and two types of memory available. The P856M is the smaller computer of the two with a maximum of 32k memory. Memory modules for this computer are 8k 16-bit words with a cycle time of 1.2  $\mu$ s. Also available are 16k 16-bit word memory modules with either 0.7  $\mu$ s or 1.2  $\mu$ s cycle time. If two 16k fast memory modules are used memory cycles interleaving is possible.

The P857M offers a tremendous increase in memory size and programming power thanks to a one-board Floating Point Processor and a one-board Memory Management Unit.

The Floating Point Processor gives a hardware execution of floating point instructions. The Memory Management Unit provides the user with two important features: it permits word and character addressing in up to 128k words memory and it implements memory protection on a 2k word page basis.

Together with a backing store, such as disc, the system offers a practically unlimited programming space and gives the user all the advantages of a real-time environment, under control of a Multi Application Monitor.

Standard memory modules are 16k 16-bit words with 0.7  $\mu$ s cycle time. On option, 16k 1.2  $\mu$ s cycle time memory modules may also be used.

The high speed memory allows interleaving when at least two 16k modules are used.

### Standard features for both CPU's are:

- 16 hardware registers of which 14 are fully programmable

- integrated V24 serial control unit

- power failure/automatic restart

- line frequency real time clock (20 ms)

- general purpose bus

- 63 program interrupt levels

- direct access for up to 256 external registers

- direct memory access facility

- microprogrammed standard instruction set

- addressing for up to 32k 16-bit words

- hardware bootstrap loader

plus the following features particular to each CPU:

#### P856M

- microdiagnostics for automatic and step-by-step testing of the first 4k words of memory and CPU-CU dialogue.

- . programmable Real Time Clock (option).

#### P857M

- microdiagnostics for automatic and step-by-step testing of the first 16k words of memory and CPU-CU dialogue.

- addressing extension for up to 128k words of memory through a Memory Management Unit MMU (option)

- memory protection on a 2k words page basis

- Floating Point Processor (option)

- programmable Real Time Clock (option).

All input/output transfers are handled via the General Purpose Bus. A comprehensive and powerful instruction set, including instructions such as multiply, divide, multiple store, multiple load, external register handling instruction and, for the P857M some extra instructions pertaining to the MMU facility, for table handling and extended memory addressing and the Floating Point Processor provide the programmer with a wide range of programming possibilities and fast execution of programs.

System software for the P856M comprises six monitors:

Basic Operating Monitor, Disc Operating Monitor, Cassette Operating Monitor, Basic Real Time Monitor, Disc Real Time Monitor, Small Real Time Monitor and a monitor extension to be used in a data communication application. The system software for the P857M is the same as for the P856M plus a Multi Application Monitor to be used in systems over 32k words.

Moreover the following processing and service software is available:

Assemblers, Linkage Editors, Overlay Linkage Editor (P857M only), FORTRAN, Real Time FORTRAN, Line Editor, Update Packages, Cassette Update, Debugging Package plus several utility packages.

BASIC (Beginners All purpose Symbolic Instruction Code) and FACT (Facility for Automation, Control and Test) conclude this wide range of software available to the user.

All system software for the P856M and P857M is compatible with the P852M system software except for the extended memory addressing software, which can only be usefully used on the P857M over 32k words.

1 General

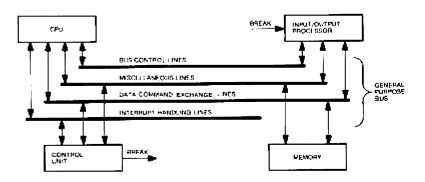

A diagramatic representation of the system's components and input/output structure are shown by figures 1.1 and 1.2 respectively.

#### THE SYSTEM

The facilities offered to a user by the P856M and P857M minicomputer systems enable each user to produce a tailor made system to suit his own requirements, and thus avoid the need to purchase facilities which will never be used.

The ease with which a system may be constructed and enhanced, and the overall flexibility of the system are centered around the general purpose bus. This asynchronous bus is used for the interconnection of the system's main components; memory, peripheral device control units, transfer facilities, interrupt facilities and the central processing unit itself. Physically the bus may be of various lengths, to suit any particular configuration, and it consists of those lines required to make correct interconnection and operation between units possible.

Efficient operation of the system is organized by a full range of controlling software in conjunction with the interrupt system. The interrupt system is capable of handling up to 63 hardware levels and operates using the necessary bus lines concurrently and independently of data transfers or bus control operations.

Peripheral connection is also made easier by use of the bus and the availability of up to 64 input/output processor sub-channels for high speed data transfers provides the system with a powerful input/output capability. Organization of the channels is on a priority basis and any number of the channels may be in operation at the same time. Once in operation the input/output processors are able to control a transfer between a device control unit and memory using both the bus and a single break line connected directly between the control unit and the input/output processor controlling the exchange.

The central processing unit, connected within the system via the bus, is normally allocated bus time in accordance with the system requirements. However, the possibility exists for the central processing unit to be given the bus whenever this is necessary for system operation. Processor instructions are available to carry out all the normal arithmetic and logical processes necessary for the operation of the system, both at word and in certain cases character level. Input/output instructions exist for the control and operation of all standard peripheral device control units and, in addition, instructions exist to read and write to external

registers via the General Purpose Bus and, for P857M extended memory addressing, instructions to Move Tables and to load registers with addresses for Page handling. The Floating Point Processor permits the use of hardware for the execution of floating point instructions.

#### Memories

The memories consist of 1.2  $\mu s$  or 0.7  $\mu s$  cycle core memory modules connected via the General Purpose Bus. The 0.7 µs memories allow interleaving. It is possible to mix the 1.2  $\mu$ s and 0.7  $\mu$ s memories.

Figure 1.1 System Main Components

Figure 1.2 Survey of peripherals and their control units

### Interleaving

Interleaving of the 0.7 µs read/write core memory permits a very fast execution of instructions. The access time comprises one read cycle after which the execution of the instruction starts immediately. To make full use of the interleaving capability the minimum memory size is 32k i.e. 2 modules of 16k where one module will contain the even addresses and the other module the odd addresses.

#### Control Panel

Operator press buttons are provided for normal manual operations, including load and read facilities to both memory and registers and an additional option is available at the control panel to enable the automatic loading and running of a bootstrap program to load any initial program. This bootstrap is held within a ROM fitted on the CPU board and is transferred to memory and executed when the IPL button is pressed.

The main facilities outlined, together with all the normal system and user facilities are covered in more detail in the following chapters.

### GENERAL SPECIFICATIONS

Microprogram controlled processor using ROM, TTL CPU Technology

circuitry.

Coincident current ferrite core memory as standard. Memory

The connection of ROM and/or PROM memory is

possible.

Core memory is available in modules of 8 and 16k for 1.2  $\mu$ s memories and in modules of 16k for 0.7  $\mu$ s memo-

ries.

Microprogram controlled test for data path, CU-CPU Microdiagnostics

dialogue, memory.

16 internal registers, 14 for general purpose use. Registers

Addressing possible for up to 64 control units and 256 External Addressing

external registers.

Up to 64 control units may be connected within the I/O Capability

Two separate types of transfer channel:

1. Programmed Channel capable of transfer rates up to 30k words/sec, depending on the method of programming used.

2. Up to 8 Input/Output Processor Channels, each controlling up to 8 separate devices on a priority basis and capable of transfer rates up 833k words/sec for memories of 1.2 µs and 1.2Mw with the fast memory. Each device control unit uses a separate break line connected directly between itself and the appropriate input/output processor.

Word Format 16-bit instruction and data word. Data may be handled

as two separate 8-bit characters.

operand, including:

- short and long constants

direct and indirect addressingaddress and operand in register

- indexing

Bus System Single asynchronous bus using TTL circuitry and in-

corporating the following subsections:

- Bus Control

- Data/Command Exchanges

- Interrupt Handling

- Miscellaneous

**Power Supply** 100V, 115V, 220V or 240V, 50Hz or 60Hz

Standard: 220V 50Hz

Environmental 0°-45°C, up to 90% relative humidity (without conden-

Conditions sation)

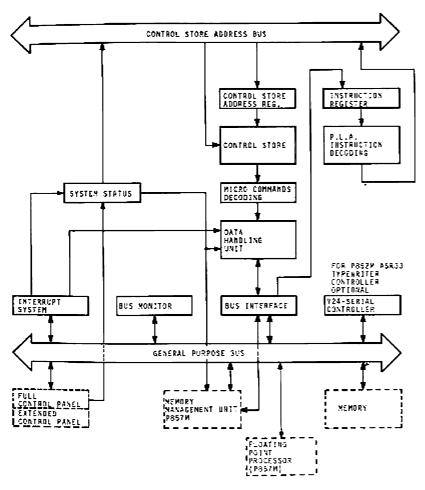

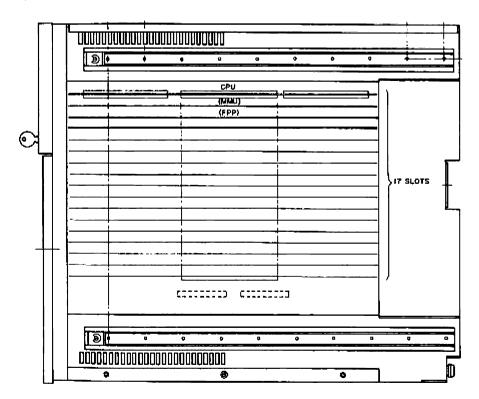

Figure 2.1 shows the main units of the system's hardware structure in block form. Explanations of the memory, GP Bus, interrupt system and input/output facilities are covered in detail in later chapters.

#### CENTRAL PROCESSING UNIT

The main components of the CPU are:

#### Arithmetic Unit (ALU)

The circuits which make up this unit enable the addition, subtraction or logical combination of the two 16-bit inputs to be available as a single 16-bit output. In addition the state of the output with reference to a positive, negative, null, or overflow condition is available, and an indication is also given when the ALU output is less than decimal 128 if this output is to be used as a memory address for stack operations. Overall control of the unit is exercised by the micro program held within the system's control ROM.

#### P Register

This register is used to hold the address of the next instruction to be carried out. It is incremented in steps of two if the program is to carry on in sequence or altered to hold the required new address if a branch is to be carried out. This register is physically only 15 bits, corresponding to bits 0 to 14 of a full 16-bit address word.

### The PSW Register

This register is divided into three parts which together form one 16-bit word known as the Program Status Word. Certain instructions and hardware functions cause this word to be stored in a memory stack whenever it is required to be saved. Program action is required to restore the saved word and whilst it is held in the memory stack program action may be carried out to alter the contents of the word.

### The PL Register

Six bits used to hold the priority level of the program that is running. Control of this register is exercised by the interrupt system.

### The CR Register

Two bits used to hold the state of the result of, or the response to, certain instructions. Control of this register is exercised by the microprogram held within the system's control ROM.

Up to eight bits which are used to record the general status of the system.

The Scratchpad

The scratchpad consists of four 15 × 4-bit read/write memory circuits arranged to give fifteen 16-bit registers A1 to A14, A15. These registers may be addressed from either the instruction being carried out or from switches on the operator's control panel. Overall control of the scratchpad is exercised by the microprogram held within the system control ROM. The specific designation of registers within the scratchpad is:

Figure 2.1 General structure of CPU

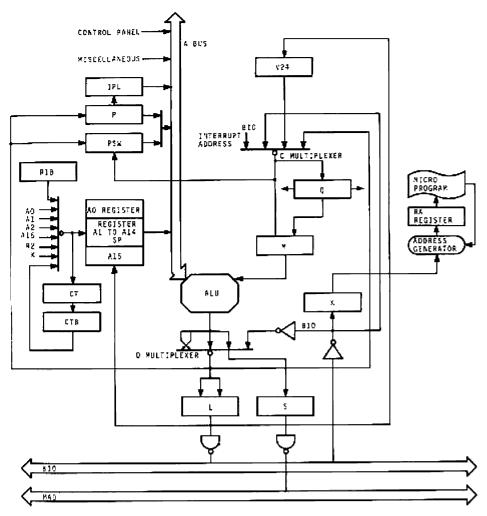

Figure 2.2 Data flow in Data Handling Unit

### Registers A1 to A14

These registers are addressed from the instruction format whilst the processor is operating and may be used to hold one or both of the operands of an instruction, and possibly the result. They may also be used as addressing and indexing registers with respect to memory.

Register A15

This register is used as a stack pointer by the interrupt system and as such it is updated whenever it is used for memory addressing. It may also be addressed from the instruction format in the same manner as registers A1 to A14.

The L Register

This 16-bit register is used as a buffer for the output of the ALU. The output from the L register is directed either to the scratchpad or to the general purpose bus, control of the register being exercised by the microprogram held within the system's control ROM.

The M Register

This 16-bit register is used as a multi-purpose register in the input/output-loop of the ALU.

The O Register

This is a 16-bit register used during double length instruction operations.

### The D Multiplexer

This multiplexer has four modes of operation:

ALU output direct output

shift right. Input to S Register

character swap

BUS input

### The C Multiplexer

This multiplexer performs operation on:

- D multiplexer output

- BIO lines output

- Short constant

- Interrupt address

- V24 scrializer output

### The S Register

This 16-bit register is used as a multi-purpose register by the addressing and counting circuits within the CPU. Control of the register is exercised by the microprogram held within the system's control ROM. The three uses of the S register are:

### Normal Addressing

Input to the S register is from the fifteen most significant bits of the output of the ALU. The output of the S register is used for memory, external register, or device addressing, via the general purpose bus. The S register must be reloaded for each change of address.

For the P857M CPU, when running in user mode, only the 12 least significant bits of the S register are sent to the General Purpose Bus, whilst the 4 most significant bits are sent to the MMU for logical to physical address translation (see page 5-1).

In system mode the 16 bits of the S register are used in the normal way.

#### Stack Addressing

The S register is initially loaded with the most significant fifteen bits from register A15, via the ALU. It is then used as a downward counter to address consecutive words in the memory stack. Addressing is carried out via the general purpose bus.

### Loop Counter

The least significant four bits of the S register are used as a loop counter for use by the system microprogram.

### The K Register

This 16-bit register is used to hold either the complete instruction or the most significant word of a double length instruction. It is the contents of this register, together with the current state of the processor, that are used to access the required microprogram words to carry out any instruction and in certain cases bits from the K register are also used directly in the control of instructions. The K register is loaded with the required instruction word from memory via the general purpose bus.

#### Address Generator GA

The input to the address generator is derived from the K register and the current state of the processor. The unit then encodes the relevant information into the address required by the control microprogram to carry out the particular instruction. The 9-bit output from the generator is input to the RA register.

### ROM Address Register RA

This 9-bit register buffers the address being used to access the current micro instruction word from the control microprogram. The register is loaded from the output of the address generator and is used directly to address the control ROM.

### Control ROM and Microprogram

This section is composed of six ROM ICs. Each IC contains 512 eight-bit words which are accessed by nine addressing inputs. Addressing from the RA register is applied in parallel to the six ICs to obtain 512, fourty-eight bit words of memory.

The microprogram is held in the ROM and exercises direct control over the data paths and timing of the CPU.

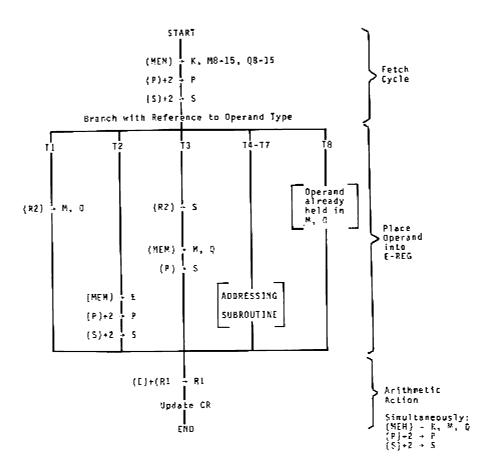

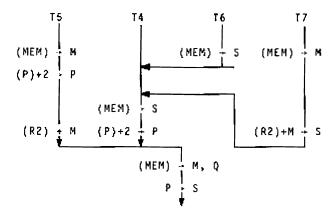

#### Control and Data Flow

The control and data flow of basic instructions is shown in Chapter 8.

### Single Precision

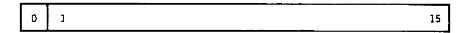

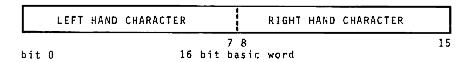

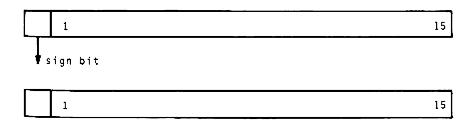

The basic word used within the system is 16 bits, and as such it may be represented by four hexadecimal symbols in the range 0000 to FFFF. Bits within the word are numbered from 0 to 15, bit 0 being the most significant bit. Data may be represented as single precision signed integer contained in one word as follows:

where bit 0 is used as the sign bit, set to zero for positive data and to 1 for negative data.

For programming purposes the word may be divided into two 8-bit characters which may be used independently by certain processor actions, bits 0 to 7 of the word representing the left hand character and bits 8 to 15 representing the right hand character.

#### Double Precision

In double length instructions data may also be represented as a double precision signed integer, contained in two words as follows:

The sign bit of the least significant word is not used and is usually set to 0. This means that 30 bits are available for data representation.

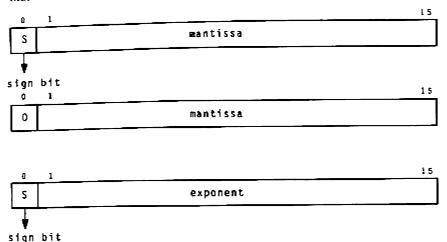

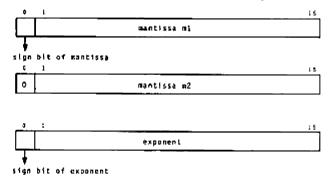

### Floating Point Data

Real numbers are place in three successive words. The first two contain the mantissa and the third the exponent.

For a more detailed description see also chapter 6 on the Floating Point Processor.

#### DATA FORMAT

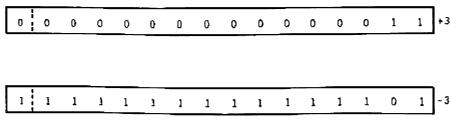

Data within a word may take the form of numeric values, logical data, or character representation. Within a word positive and negative numeric values are able to be represented, the most significant bit, bit 0, of the word being used to indicate the sign of any value. Positive values are represented by making the sign bit equal to 0 and using the remaining fifteen bits to express the numeric value in binary. Negative values are represented by making the sign bit equal to 1 and expressing the required numeric value by its 2's complement in the remaining fifteen bits.

The figure below shows the representation of the numeric values +3 and -3 within the data word.

Representation of Numeric Values

Numeric values represented and used within characters may only specify positive values to a maximum of 8 binary bits, no sign bit being used by either character.

Logical data may be held and used in either whole word or character format and no sign bit is used, data being bit significant within the complete word or character.

Data representing standard alphanumeric and control characters may be held within the separate characters of the data word and will be treated as either numeric values or logical data depending on the instructions carried out when using such data.

Core memory is available in modules of 8k or 16k 16-bit words with a cycle time of  $1.2~\mu s$  or  $0.7~\mu s$  up to maximum of 32k for the P856M and 128k for the P857M. Each module consists of a single printed circuit board which is mounted within the mounting box. Connection to the system is by pluggable connectors to the General Purpose Bus and provision is made for the protection from loss or detorioration of data during power on/off sequences and in the event of any power failure.

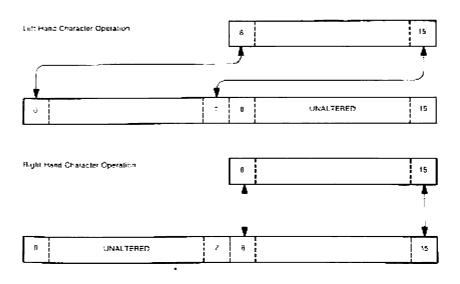

All memory modules offered are able to operate in either word or character mode and special character handling instructions are available to provide a useful and efficient facility with respect to character buffering and transfers. Character mode operation enables the contents of the least significant eight input/output lines to be either set from, or written into either the left hand or right hand character of the addressed memory location. In all such operations the unused character is left unaltered.

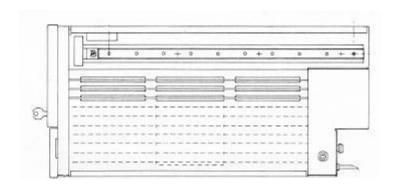

Figure 4.1 Operation of memory in character mode

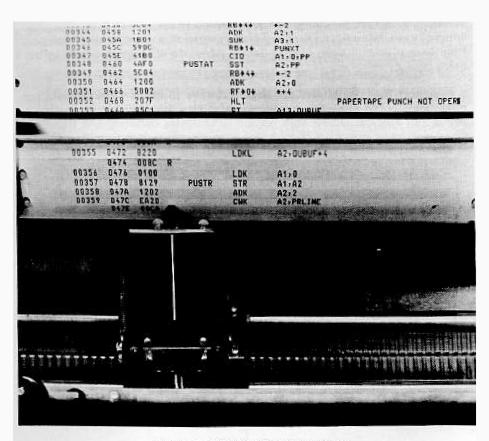

Listing on PER 3100 matrix printer.

#### MEMORY ADDRESSING

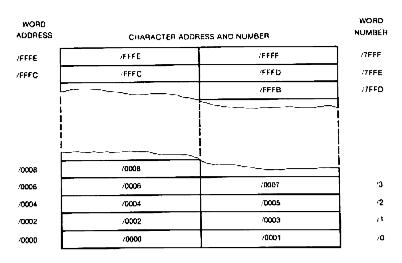

Depending upon the type of instruction or operation being carried out the memory may be addressed in words or characters for programming purposes. Bits 0 to 14 of the address are used to access memory in word mode, bit 15 being unused and insignificant. When operating in character mode all sixteen address bits are used, bits 0 to 14 addressing the word location required and bit 15 addressing the character. With bit 15 set to 0 the left hand character is addressed, bit 15 set to 1 addresses the right hand character.

Figure 4.2 Layout of words and characters in memory.

Word addresses written with the least significant bit present will be addressed ignoring this bit.

Memory addressing in an environment > 32k is entirely transparent to the user and is taken care of by the Memory Management Unit.

#### DESCRIPTION

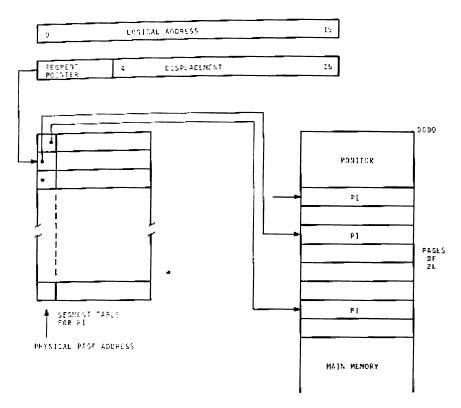

The Memory Management Unit is a feature of the P857M computer which uses Virtual Addressing and allows to extend memory addressing over 32k op to 128k words. It permits dynamic program relocation in multitask programming under control of the Multi Application Monitor and offers a memory protection facility. The MMU cannot by used with the P856M.

Special instructions are required by the MMU to handle the memory addressing.

The system considers the memory as consisting of n blocks of 2k words, called pages. The monitor is always loaded at the beginning of memory from the lowest address upwards. When the user program is called it is loaded behind the monitor and it is split in pages of 2k, which do not need to be contiguous. Moreover, only those parts of the program are loaded which are required at the time.

A user program may not exceed 32k words.

In order to address the pages in memory a segment table of  $16 \times 16$  bits is built for each program called.

The user program uses relative addresses contained in 16 bits. At execution time these logical addresses are divided in two parts. One part, bits 0 to 3 included, contain a segment address and bits 4 to 15 included contain the relative address from the beginning of the page.

The segment address refers to an entry in the segment table and the MMU translates the entry, pointed to by the 4-bit segment address, into a 6-bit physical page number which, together with the 12-bit displacement value, produces an 18-bit address.

If the running program has less than 16 pages loaded in memory the unused words of the segment table have a protection bit set.

In system mode, see page 13-10, the MMU does not translate the 4-bit segment addresses as the system software routines use absolute addresses.

To transfer in this mode data from a system to a user area special instructions which have a source table address, destination address and length as parameters, permit to communicate between the user and system areas.

Figure 5.1 MMU Operation.

## Layout of segment table word

The MMU and the operating system control the contents of the segment table words. The bits in this word have the following meaning:

bits 0-5 Physical Page address.

Page Error indication

Page Error indication. This bit is set by the Operating System for those pages which do not belong to the addressing environment of the running program. By checking this bit the MMU activates a 'Page Fault' signal when a wrong or missing page is tried to be accessed.

This bit is not used for system programs.

bit 7 Read Only page. This bit is set when the relevant page is protected against overwriting. This feature allows to share the page among several user programs.

- bit 8 Modified Page. This bit is set by the MMU when a write operation took place in this page. If so, the page need to be swapped out again to the backing store before a new page is loaded. If the bit remains zero the page may be overwritten which saves time.

bit 9 Overflow. The setting of this bit depends on the value in bits 10-15 included.

- bits 10-15 Counter. A 6-bit counter is associated with each page descriptor. All counters are incremented at regular time intervals. This interval, which depends on the memory speed, is chosen at system generation time in a ratio 1 to 256. During execution of a program, each time a page of the running program is called the counter is reset to zero. If a counter reaches the interval set an overflow bit is set. When space in memory is required the Operating System swaps out those pages which have the overflow bit set.

### Page Fault handling

A special interrupt *Page Fault* is given when an attempt is made to write into a protected page or when a missing or wrong page is tried to be accessed. The interrupt line is wired from the MMU to the CPU and it has a priority over other internal or external interrupts.

If a fault is detected the execution of the running instruction is stopped and if necessary, exchange parameters are updated to resume the execution later on. Moreover three words are stored in the system stack:

- the address of the instruction which caused the page fault interrupt

- the PSW

- a word containing the page address of the page in which a fault was detected and a MMU program level coded on the MMU board.

Next the CPU is switched to the Inhibit state and the computer to system mode. The MMU program level is loaded in the PLR register and a branch is made to an interrupt routine address.

The interrupt routine does not require an RIT instruction to reset the interrupt as the Page Fault interrupt is automatically deactivated.

#### Introduction

The Floating Point Processor is an optional, high speed arithmetic processor which may be included in the P857M system.

It performs by hardware, single precision, all floating point arithmetic operations. The processor is contained on one board and must be plugged in the *third* slot of the M4 or M5 mounting box, also when no Memory Management Unit is used. The power consumption is  $\pm 5$  V, 6.0 Amps.

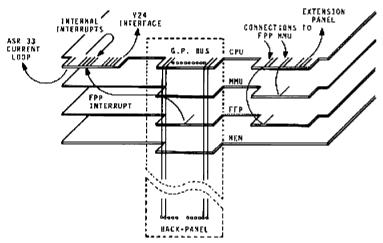

Figure 6.1 shows the connection of the FPP in the system.

Figure 6.1 Connection of Floating Point Processor

## Operation

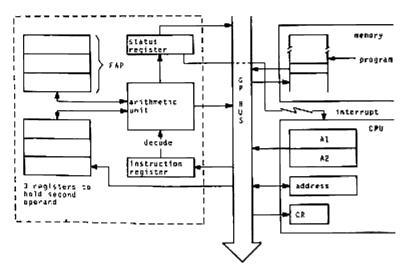

The board contains three 16-bit accumulators FPA holding the result of a floating point operation or the floating point operand or the first floating point operand where the second floating point operand is temporarily placed in three other 16-bit registers.

Program instructions are fetched and decoded by the CPU. The significant bits of each instruction, i.e. op.code, mode, bits etc. are also copied in an instruction register on the FPP board.

When a floating point instruction is encountered in the program the Floating Point Processor is activated by the CPU and the latter stops.

Some decoding of the instruction register contents takes place on the FPP board

and an arithmetic unit on this board is signalled the type of operation it has to perform.

The arithmetic unit takes the information to be operated upon from the contents of the FPA, registers A1 and A2, the contents of consecutive memory locations.

The result is stored in FPA, or A1 and A2, or a number of consecutive memory locations.

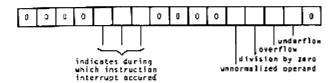

During or immediately after the execution a status register is reset to either zero (no errors) or bits in this register are set to 1. The contents of the status register may be:

Any abnormal condition gives an FPP interrupt and sets the CPU condition register to 3. The FPP interrupt must be connected to one of the eight internal interrupt levels.

If no error condition was obtained the CPU fetches the next instruction.

Figure 6.2 gives the architecture and flow in the FPP.

Figure 6.2 Floating Point Processor

### Floating Point Format

The Floating Point Processor handles data of the following format:

## Floating Point Data

Floating Point Data are real numbers contained in three consecutive 16-bit words. The first two words contain the mantissa which is a left normalized, double precision number.

The exponent is held in the third word as a single precision integer.

The sign bit of the second mantissa word is always zero. The mantissa scale is between:

positive:

$$\pm \frac{1}{2} \le m \le 1^{-\epsilon}$$

where  $\epsilon = 2^{-30}$

negative:  $-1 \le m \le -\frac{1}{2} - \epsilon$

The exponent scale is between:  $-2^{15} \le E \le +2^{15} - 1$

A floating point number is:  $(m1,m2) \times 2^E$ , where E = the exponent. The absolute value is:  $| DATA | < 10^{9868}$ . The accuracy is in 9 decimal digits.

The Floating Point Processor also allows the conversion of floating point data to integer format and vice versa.

In that case the Processor permits operations with single precision integers (on 16 bits) and double precision integers (on 32 bits, the most significant bit of the second word being 0).

## Floating Point Instructions

Floating Point Instructions use the same type of addressing modes as the remainder of the P857M instruction set.

A survey of the Floating Point Instruction Set is:

- FFL Convert the double precision integer to a floating point operand. Store the result in FPA.

- FFX Convert a floating operand in FPA to a double precision integer. The result is placed in A1 and A2.

- FADR Add the floating point operand in FPA to the floating point operand in three consecutive memory locations. The first address is indicated by the contents of the specified register. The result is either placed in FPA or in memory.

- FAD Add the floating point operand in FPA to the floating point operand in three consecutive locations. The first address is indicated by the address in the instruction. The result is placed in FPA or in memory.

- FSUR Subtract the floating point operand in three consecutive memory locatons, the first address is indicated by the register in the instruction, from the floating point operand in FPA. The result is placed in FPA or in memory.

- FSU Subtract the floating point operand in three consecutive memory locations, the first address is given by the address in the instruction, from the floating point operand in FPA. The result is placed in FPA or in memory.

- FMUR Multiply the floating point operand in FPA by the floating point operand in three consecutive memory locations, whose first address is given by the register in the instruction. The result is stored in FPA or in memory.

- FMU Multiply the floating point operand in FPA by the floating operand in three consecutive memory locations, whose first address is pointed to by the address in the instruction. The result is stored in FPA or in memory.

- FDVR Divide the floating point operand in FPA by the floating point operand in three consecutive memory locations, whose first address is given in the register specified in the instruction. The result is placed in FPA or in memory.

- FDV Divide the floating point operand in FPA by the floating point operand in three consecutive memory locations, whose first address is pointed to by the address in the instruction. The result is placed in memory or in FPA.

- FLDR The contents of three consecutive memory locations are placed in FPA. The first memory location is indicated by the register in the instruction.

- FLD The contents of three consecutive memory locations are placed in FPA. The first memory location is pointed to by the address in the instruction.

- FSTR The contents of FPA are stored in three consecutive memory locations. The first address is indicated in the register in the instruction.

- FST The contents of FPA are stored in three consecutive memory locations. The first location is pointed to by the address in the instruction.

See Chapter 7 for instruction execution times.

7 Instructions

The instruction set gives the programmer the ability to carry out all the functions necessary to program the system efficiently and may be divided into ten basic groups:

Load/Store Instructions

Arithmetic Instructions

Logical Instructions

Character Instructions

Branch Instructions

Shift Instructions

Control Instructions

Input/Output Instructions

External Transfer Instructions

Move Table Instructions

Within these groups efficiency is ensured by the possible use of up to eight different methods of forming one of the instruction's operands, the method to be used being chosen by the programmer with reference to the memory and timing requirements of any particular program.

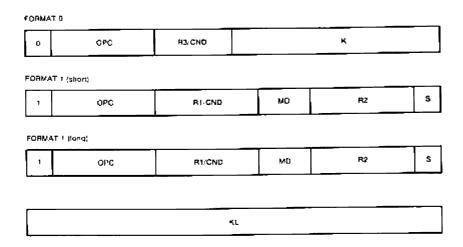

Two formats for instruction layouts are used and where necessary two words are used to define an instruction.

#### INSTRUCTION FORMATS

Two instruction formats are possible and these are defined within the instruction by the most significant bit, bit 0, of the instruction word. Where instructions consist of two words the format bit is the most significant bit of the first word only.

Format 0 instructions are always short, that is one word. Format 1 instructions may be short or long, one or two words.

Figure 7.1 Layout of instruction formats.

OPC 4 bits, the pattern of which defines the instruction to be carried out.

- R1 4 bits, specifies the working register to be used by the instruction, A0 A15. It may contain one of the operands to be used and may also be used to hold the result of the instruction. In certain cases with R1 = 0 the addressed register, the P register, will not be used and in these cases R1 = 0 will qualify the operation code and define a different instruction than when R1 = 0.

- R2 4 bits, specifies the second working register to be used by the instruction A1 A15. It may contain the second operand or hold an address to be used in forming this operand. If R2 is made zero, no second working register is specified but this condition is used in deciding the method of forming the second operand.

- R3 3 bits, specifies the working register to be used by the instruction A0 A7. It may contain one of the operands to be used and may also be used to hold the result of the instruction. In certain cases with R3 = 0 the addressed register, the P register, will not be used and in these cases R3 = 0 will qualify the operation code and define a different instruction than when R3 = 0.

- CND 3 bits, specifies the condition which must exist for a particular instruction to be carried out. Used to qualify conditional branch instructions and replaces R3 or the most significant 3 bits of R1.

- MD 2 bits, specifies the mode of addressing to be used when forming the second operand of an instruction where this is applicable.

- S I bit, applicable to certain instructions using memory. When present it specifies that the result of the instruction concerned is to be stored in the memory address specified by the instruction. When this bit is not present the result is placed into the working register specified by R1.

- 8 bits, these bits are used to specify the operand in format 0 instructions, and include short constant operands (k) and short displacements (m-for relative branch instructions). This field is also used to specify counts for shift instructions (n) and device addresses to I/O instructions (dev), in these cases a part of the field may be used to qualify the operation code.

- KL 16 bits, this field is made up of the complete second word of a double length instruction and may specify a long constant (KL) or an address (m).

# FORMING THE OPERAND

Many of the instructions may use various methods of forming one of the operands to be used. In all, eight methods of forming an operand are available governed by the values of the Format, Mode, and R2 fields of the instruction layout.

Figure 7.2 lists the eight methods of forming an operand and a brief description of each method is given following the figure.

| Type                                   | Format                               | Mode                                  | R2                                   |                                                                                                                |

|----------------------------------------|--------------------------------------|---------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------|

| T1<br>T2<br>T3<br>T4<br>T5<br>T6<br>T7 | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>0 | 00<br>01<br>01<br>10<br>10<br>11<br>- | R2 ≠ 0<br>R2 = 0<br>R2 ≠ 0<br>R2 ≈ 0 | Reg/Reg. Long Constant Address in Reg R2 Address in next word Indexed Indirect Indexed Indirect Short Constant |

Figure 7.2

## Tt. Register/Register - Format 1 (short)

The operand is the value in the register specified by R2 of the instruction format.

# T2. Long Constant - Format 1 (long)

The operand is the value in the least significant word, all sixteen bits, of the double length instruction format.

# T3. Address in Register - Format 1 (short)

The operand is held in memory. The memory address of the operand is the value in the register specified by R2 of the instruction format.

# T4. Address in Next Word - Format 1 (long)

The operand is held in memory. The memory address of the operand is the value in the least significant word of the double length instruction.

# T5. Indexed Address in Next Word - Format 1 (long)

The operand is held in memory. The memory address of the operand is found by adding the value in the register specified by R2 of the instruction format to the value in the least significant word of the double length instruction.

## T6. Indirect Address in Next Word - Format 1 (long)

The operand is held in memory. The memory address of the operand is also held in memory. This indirect address is the value in the least significant word of the double length instruction.

## T7. Indexed Indirect Address in Next Word - Format 1 (long)

The operand is held in memory. The memory address of the operand is also held in memory. This indirect address is found by adding the value in the register specified by R2 of the instruction format to the value in the least significant word of the double length instruction.

### T8. Short Constant - Format 0

The operand is the value in the least significant eight bits of the instruction format.

### INSTRUCTION TIMING

The timing of the instructions depends on various factors: the type of instruction itself, the memory, the method of forming the operand and the number of memory cycles required.

The instruction set offers the possibility of very rapid execution times where single word register/register or short constant operations are employed whilst the more complex register/memory instructions save execution time when compared with the routines they may replace.

Execution time is also reduced in the case of conditional instructions by carrying out the conditional check immediately after accessing the instruction and then only continuing if the required conditions are satisfied.

#### TRAP ACTION

The use of any invalid instruction causes the activation of the Trap action which consists of the following basic actions:

- the CPU does not attempt to carry out the instruction

- information with reference to the instruction address and processor status is saved in the stack

- interrupts are inhibited

- a user mode flag is reset when working in user mode

- an indirect branch is made to address /7E for a trap routine.

#### THE INSTRUCTION SET

The instructions within the basic groups, together with their mnemonic, addressing type(s) and the execution time for the different types of memory are listed here:

| Load/Store Instructions |                                                           | Addressing                  | Execution times in $\mu$ s                   |                                              |

|-------------------------|-----------------------------------------------------------|-----------------------------|----------------------------------------------|----------------------------------------------|

|                         | -                                                         | types                       | 1.2 µs memory                                | 0.7 <i>μ</i> s memory                        |

| LD<br>LDR<br>LDK        | Load<br>Load Register<br>Load Constant                    | T4 - T7<br>T1, T3<br>T8, T2 | 3.7 - 5.0 μs<br>1.4 - 2.5 μs<br>1.3 - 2.5 μs | 2.2 - 3.0 μs<br>1.2 - 1.8 μs<br>0.9 - 1.5 μs |